#### HDL LAB

## B.E., V Semester, ELECTRONICS & COMMUNICATION ENGINEERING / TELECOMMUNICATION ENGINEERING [As per Choice Based Credit System (CBCS) Scheme]

| Course Code          | 17ECL58                                                     | CIE Marks  | 40 |

|----------------------|-------------------------------------------------------------|------------|----|

| Number of<br>Lecture | 01 Hr Tutorial (Instructions)<br>+ 02 Hours Laboratory = 03 | SEE Marks  | 60 |

| Hours/Week           |                                                             |            | 03 |

| RBT Levels           | L1, L2, L3                                                  | Exam Hours | 03 |

#### CREDITS - 02

Course Objectives: This course will enable students to:

- Familiarize with the CAD tool to write HDL programs.

- Understand simulation and synthesis of digital design.

- Program FPGAs/CPLDs to synthesize the digital designs.

- Interface hardware to programmable ICs through I/O ports.

- Choose either Verilog or VHDL for a given Abstraction level.

Note: Programming can be done using any compiler. Download the programs on a FPGA/CPLD boards such as Apex/Acex/Max/Spartan/Sinfi or equivalent and performance testing may be done using 32 channel pattern generator and logic analyzer apart from verification by simulation with tools such as Altera/Modelsim or equivalent.

## Laboratory Experiments

### Part-A: PROGRAMMING

- 1. Write Verilog code to realize all the logic gates

- 2. Write a Verilog program for the following combinational designs

- a. 2 to 4 decoder

- b. 8 to 3 (encoder without priority & with priority)

- c. 8 to 1 multiplexer.

- d. 4 bit binary to gray converter

- e. Multiplexer, de-multiplexer, comparator.

- 3. Write a VHDL and Verilog code to describe the functions of a Full Adder using three modeling styles.

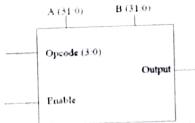

- 4. Write a Verilog code to model 32 bit ALU using the schematic diagram shown below

- ALU should use combinational logic to calculate an output based on the four bit

- ALU should pass the result to the out bus when enable line in high, and tri-state the out bus when the enable line is low.

- ALU should decode the 4 bit op-code according to the example given below.

| OPCODE | <b>ALU</b> Operation |

|--------|----------------------|

| 1.     | A+B                  |

| 2.     | A-B                  |

| 3.     | A Complement         |

| 4.     | A*B                  |

| 5.     | A AND B              |

| 6.     | A OR B               |

| 7.     | A NAND B             |

| 8.     | A XOR B              |

- 5. Develop the Verilog code for the following flip-flops, SR, D, JK and T.

- 6. Design a 4 bit binary, BCD counters (Synchronous reset and Asynchronous reset) and "any sequence" counters, using Verilog code.

# Part-B: INTERFACING (at least four of the following must be covered using VHDL/Verilog)

- 1. Write HDL code to display messages on an alpha numeric LCD display.

- 2. Write HDL code to interface Hex key pad and display the key code on seven segment display.

- 3. Write HDL code to control speed, direction of DC and Stepper motor.

- 4. Write HDL code to accept Analog signal, Temperature sensor and display the data on LCD or Seven segment display.

- 5. Write HDL code to generate different waveforms (Sine, Square, Triangle, Ramp etc.,) using DAC change the frequency.

- 6. Write HDL code to simulate Elevator operation.

#### Course Outcomes: At the end of this course, students should be able to:

- Write the Verilog/VHDL programs to simulate Combinational circuits in Dataflow, Behavioral and Gate level Abstractions.

- Describe sequential circuits like flip flops and counters in Behavioral description and obtain simulation waveforms.

- Synthesize Combinational and Sequential circuits on programmable ICs and test the hardware.

- Interface the hardware to the programmable chips and obtain the required output.

### Conduct of Practical Examination:

- 1. All laboratory experiments are to be included for practical examination.

- 2. Strictly follow the instructions as printed on the cover page of answer script for breakup of marks.

- 3. Change of experiment is allowed only once and Marks allotted to the procedure part to be made zero.

D,V.

H.O.D.

Dept. Of Electronics & Communication Alva' Institute of Engg. & Technology Mijar, MOODBIDRI - 574 225